Project update 14 of 17

The NUT2NT+ FPGA Slave FIFO Makes the Signal Capturing Stable

Hello to Everyone!

There are updates to the code of the Lattice FPGA and FX3 USB microcontroller.

There were samples losses in high input/output or CPU load situations. We added a slave FIFO buffer in FPGA, changed Cypress GPIF design and now continuous capturing become more stable in real apps. Now thanks to slave FIFO buffer the samples are accumulated in FPGA and then the FX3 microcontroller downloads bulk of data when FIFO contains necessary number of samples.

People already having the NUT2NT+ can download the code from Amungo github, build the FPGA and FX3 binaries and test it under high system load.

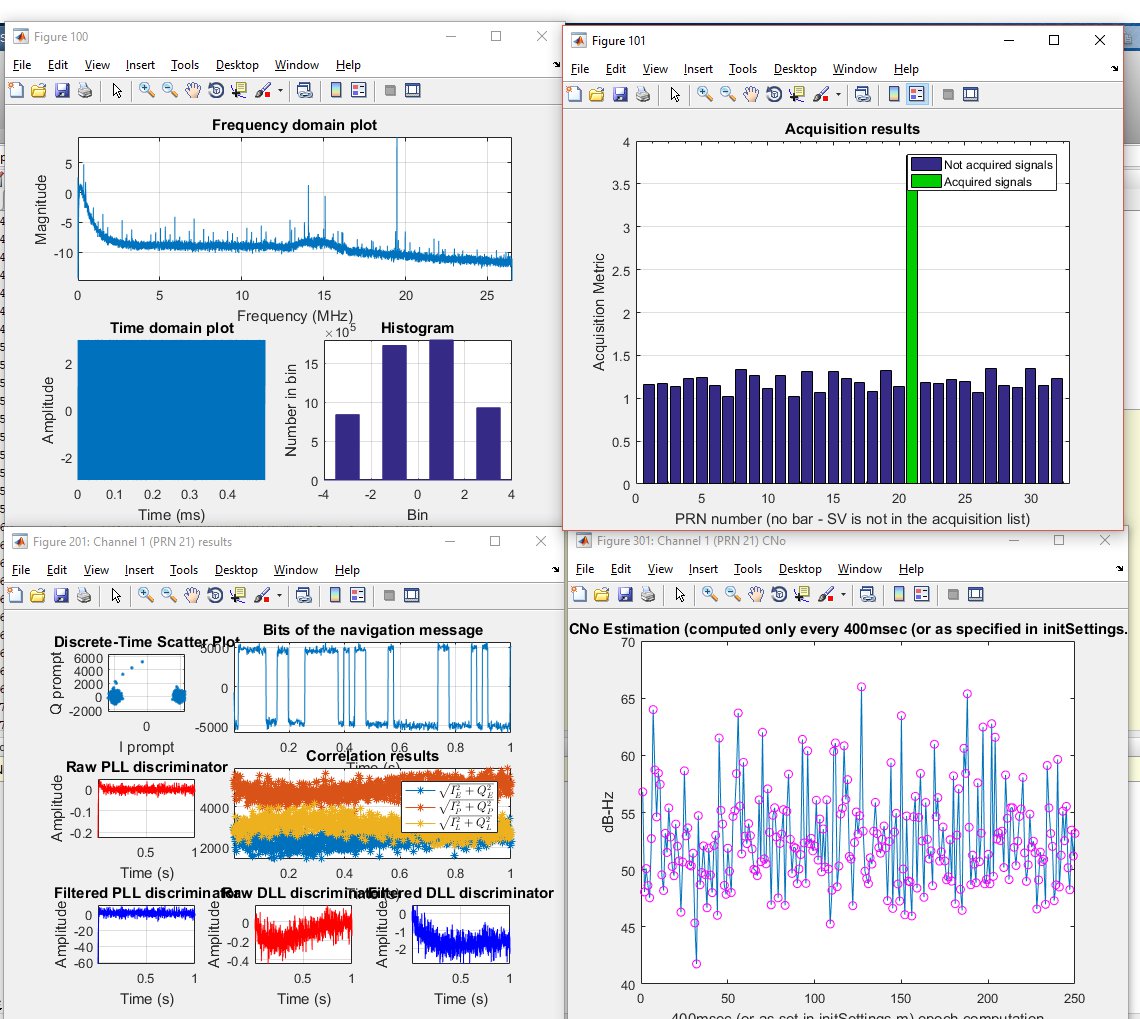

We captured long signal sample and processed it by Matlab code. Alright, the SNR value is about 50 dB all the time.

The NUT2NT+ and antenna used in test above and oscilloscope used to debug the FPGA code.

Artem Krivosheev,

Amungo Navigation