Project update 6 of 8

Driving Multiple Miners & Using Our Integrated Board Utility Library

by Xiaosen JiangDriving Multiple FPGA Miners with a Single Host

We have been asked whether our host software supports the use of multiple miners. The answer is yes. In fact, it auto-detects all UltraMiner FPGA devices connected through USB to the host and distributes tasks to each individual miner once a connection to the mining pool server has been established. In theory, a single host device should support one UltraMiner for each serial COM port provided by its operating system. There is one caveat, however: UltraMiner draws about 0.6 A from the USB port, so you should ensure that you have a high-quality USB hub if you plan to connect multiple miners.

The video below shows a single Raspberry Pi driving two UltraMiners:

Fully Integrated Board Utility Library

We recently finished integrating all board utility methods into a single shared library. This library provides methods to program the FPGA bitstream file and to hard reset the FPGA, the PMIC control, and status monitoring. Below is a snippet that shows the various functions provided by the board utility library. It is still quite crude, but we will be adding more features in the future.

/* FPGA flash chip access routines

* erase and program the bitstream file to the flash chip */

EXPORT_DLL int program_flash_chip(FLASH_DEVICE_OBJECT * pfdo, uint32 startAddr, char *filename)

EXPORT_DLL int erase_flash_chip(FLASH_DEVICE_OBJECT * pfdo)

/* This function issues a hard reset to FPGA chip,

* upon reboot, fpga will reconfigure using the bitstream file stored in flash chip */

EXPORT_DLL int reset_fpga(void);

/* PMIC access routines */

/* set the core output voltage */

EXPORT_DLL int set_vout(void * fth, float vout);

/* PMIC monitoring routines, reading the voltage, current load and temperature */

EXPORT_DLL float read_vout(void * fth);

EXPORT_DLL float read_iout(void * fth);

EXPORT_DLL float read_temp(void * fth);

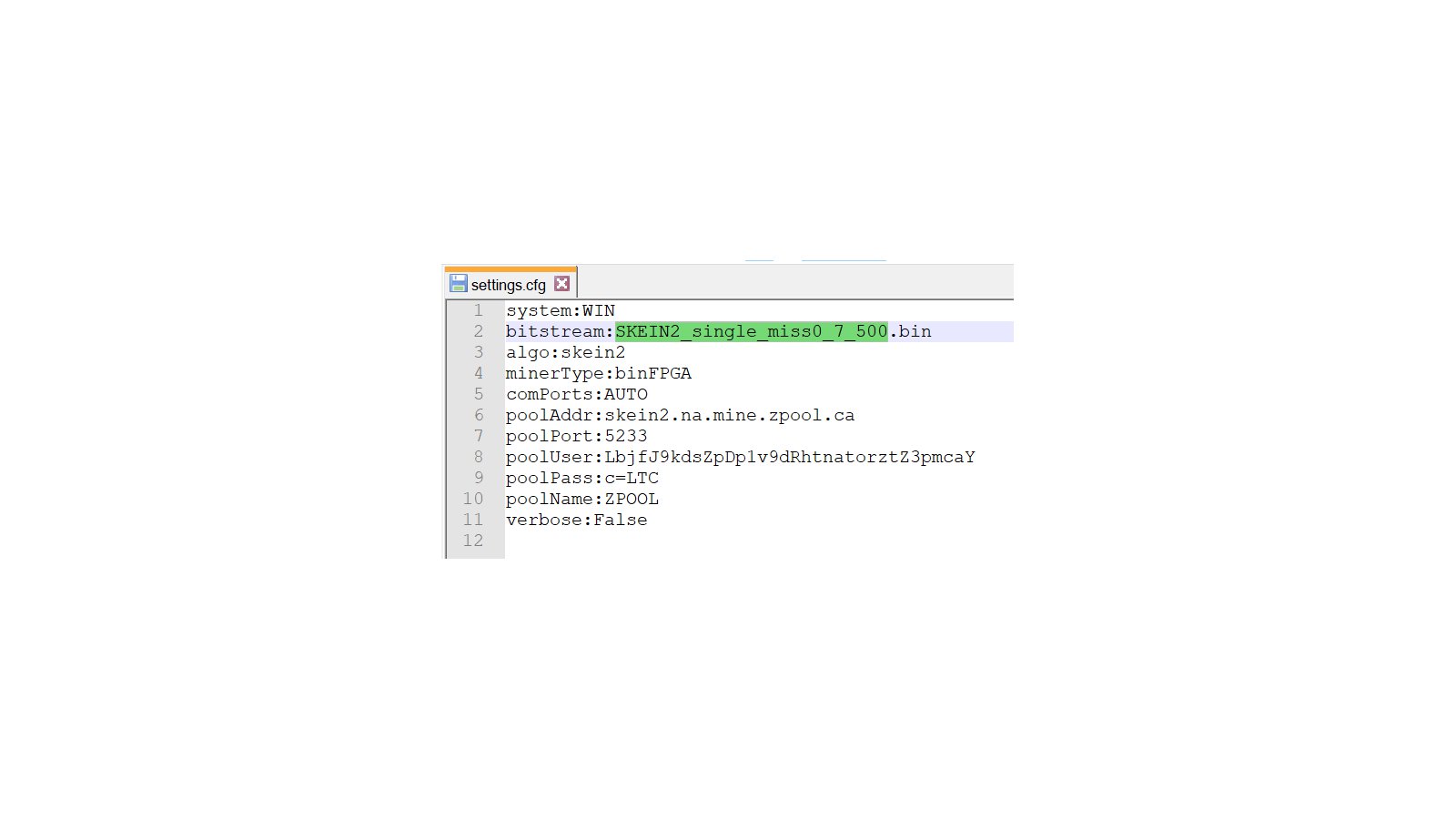

To test this library, we integrated it into our host software and used it to manage dynamic voltage control and monitoring, as shown in the video we posted last week. More recently, we added functionality that allows the host software to flash an FPGA bitstream file specified in the configuration:

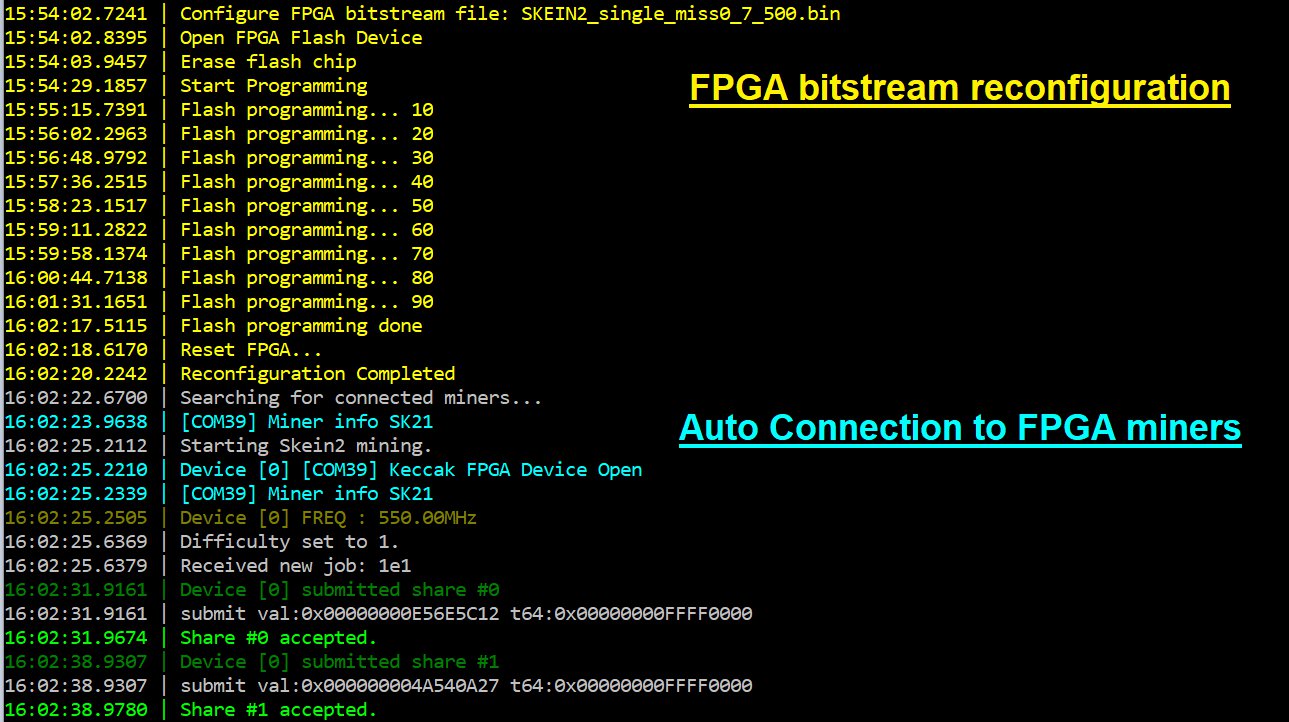

The host software loads and flashes the bitstream file on startup, then hard resets the FPGA and reconfigures it to use the new bitstream. As you can see below, it successfully detected the attached UltraMiner.

Using this feature, we can fully automate remote mining, even for algorithms (like ODOcrypt) that require periodic updates. Furthermore, new FPGA bitstream files can be introduced with minimal interruption to the mining operation.