PCIe Update for Developer Edition

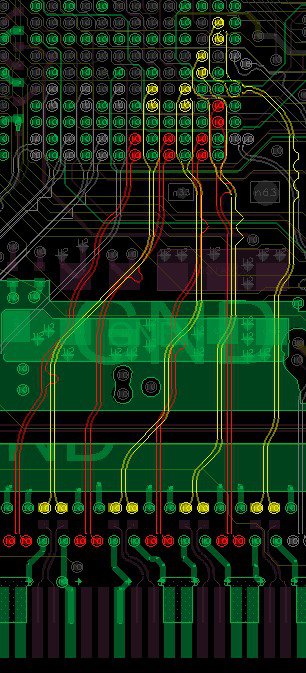

Our team is hard at work adding features to the UltraMiner FPGA Developer Edition. The four high-speed TX and RX lanes for PCIe are already routed with solid ground reference, as shown in the figure below. TX and RX are routed on different layers to reduce interleave crosstalk. The overrall routing length is less than 1.5 inch, which will help ensure good signal quality for high speed data transmission.

GPIO Connector Update for Developer Edition

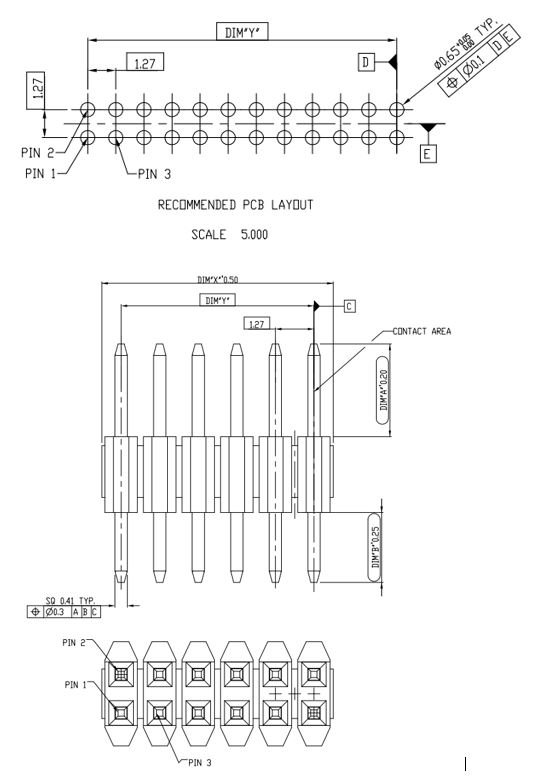

Based on input from our backers, we have changed the GPIO connector pitch from 2.54 mm to 1.27 mm. (The development board uses Amphenol’s 20021111-00026T4LF.) This modification helped us cut the connector area by half while improving the differential signal coupling between P and N within a pair. Signal intergrity for high speed GPIO is greatly improved as a result. Pin pitch and height information are shown in the figure below.