RHS Research LLC

FPGA Boards

AMD

RHS Research LLC

FPGA Boards

AMD

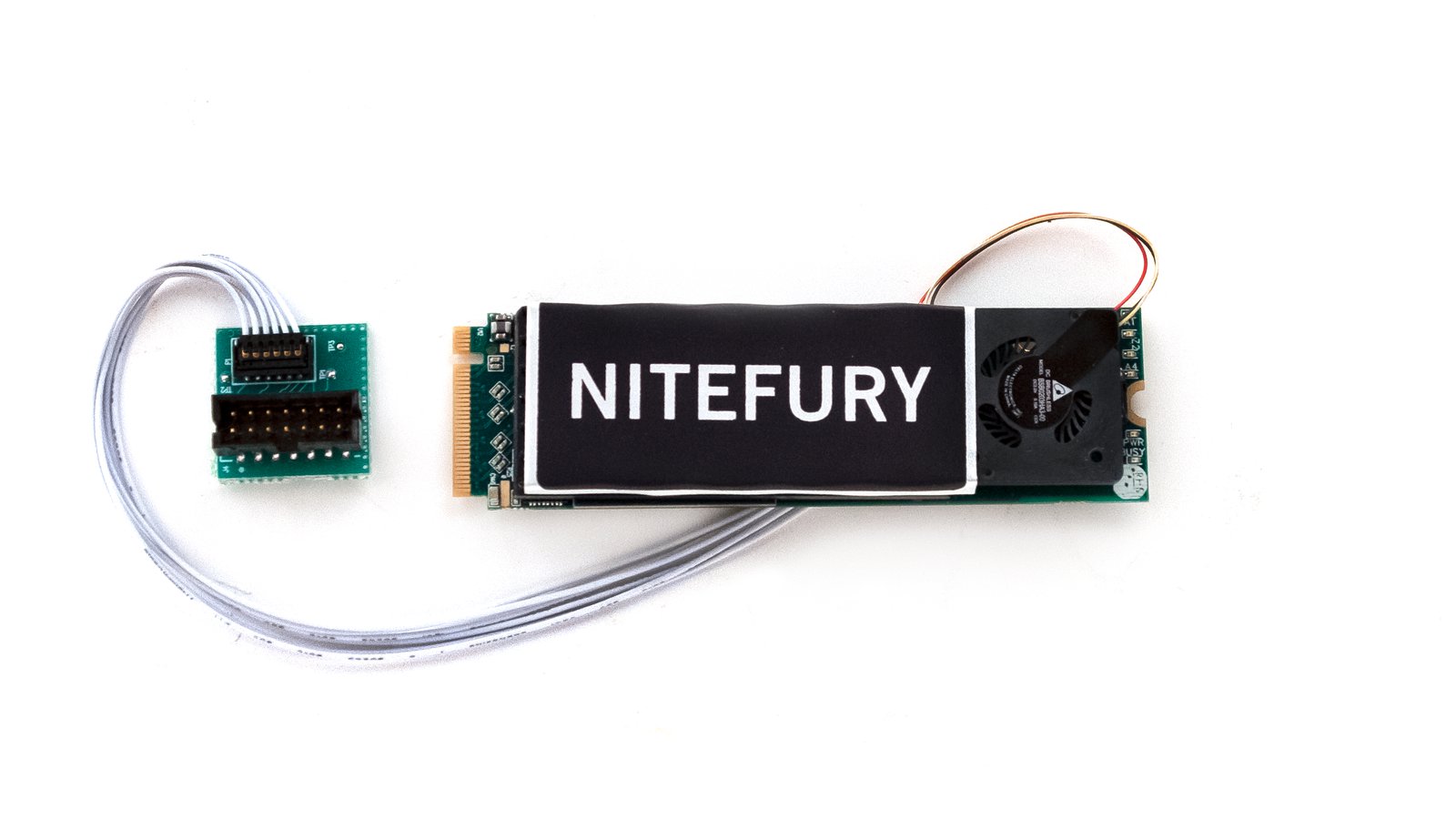

NiteFury is an Artix-7 FPGA development board in an M.2 form-factor that includes on-board DDR3 RAM. This combination lets you work with PCI Express at incredible rates from inside your laptop or desktop. You can also use NiteFury as an FPGA co-processor. Let Xilinx’s largest Artix-7 handle your encryption or act as a hardware-level encoder/decoder for speedy workflows. It’s your FPGA, design what you like.

NiteFury is designed for seriously fast PCIe design prototyping. But essentially, it’s an FPGA (with RAM) inside your computer. So anything you can do with an FPGA, you can do quickly with NiteFury. Just design for your need in Vivado.

Some fun things you could do:

NiteFury is open source hardware: https://github.com/RHSResearchLLC/NiteFury

The optional, custom-made NiteFury heatsink allows you to work the Artix-7 FPGA even harder before having to worry about heat buildup. It allows for about 8 W of power dissipation to reach a 100°C junction temperature at an ambient temperature of 25°C. It’s also only 5 mm tall by itself. Mounted to the board, the total height is 10 mm. The heatsink is permanently attached to the NiteFury board.

A heatsink is an absolutely necessity when using NiteFury, so you can either use your own or purchase your unit with the heatsink option.

Note: When using the integrated heatsink, make sure you have at least 7.5 mm of clearance above the top of the board. Not all laptops have this much clearance.

| Feature | NiteFury | PicoEVB |

|---|---|---|

| FPGA | Xilinx Artix XC7A200T | Xilinx Artix XC7A50T |

| Logic Cells | 215K | 52K |

| On-board RAM | 512 MB DDR3 | None |

| Form Factor | M.2 (NGFF) 2280, keyed for M slot | M.2 (NGFF) 2230, keyed for A and E slots |

| Dimensions | 22 x 80 x 5.5 mm (without heatsink) | 22 x 30 x 3.8 mm |

| Host Interface | PCIe 4x gen 2 | PCIe x1 gen 2 |

| Built-in JTAG | No | Yes |

| External Interface | 12 total I/O, 4 selectable analog or digital | No |

| User-controllable LEDs | 4 | 3 |

Having successfully fulfilled orders for PicoEVB, a very similar product in terms of manufacturing, we’re well positioned and prepared for the next iteration - NiteFury.

Shortly after the crowdfunding goal is met, we’ll place orders for the components with the longest lead time, namely, the FPGA.

Units will be shipped to backers from Crowd Supply, so packages will be sent from Portland, Oregon. Shipping to the United States is included in the price of NiteFury. Delivery outside the US will incur a surcharge during checkout. For more information, please see Crowd Supply’s guide on ordering, paying, and shipping.

NiteFury design is complete and prototype-verified, so most of the risk to the project is that which is inherent in any electronics manufacturing. Components could have unanticipated shortages, leading to longer turn-times. There could be errors in the first production run of PCBs or in assembly. Shipping could take longer than expected, damage could occur, or even a shipping loss. But these potential scenarios all have methods of recovery. And, importantly, we’ll keep backers apprised via project updates should any of them occur.

"If you want some serious machine-learning grunt, then pick one of these M.2-based FPGA boards."

Produced by RHS Research LLC in Syracuse, NY.

Sold and shipped by Crowd Supply.

NiteFury with an integrated, permanently installed, low profile heatsink and fan for about 8 W of power dissipation.

The original NiteFury, with the largest Artix FPGA and 4 Gb DDR3.

RHS Research LLC is a small company located in upstate NY, focused on bringing low-cost FGPA development kits to makers and hobbyists.